案例應用 | ACEM在大規模數據中心、人工智能和深度學習、高算力領域的應用:系統鏈路并行信號完整性分析與仿真

PART1 適配行業

ACEM是由芯瑞微(上海)電子科技有限公司,基于自主知識產權技術開發的三維電磁仿真軟件。

作為任意三維結構全波電磁仿真工具,ACEM依托強大的3D編輯、自動參數化和極低的內存占用特性,搭載imesh智能加密和網格后處理引擎,高性能的GPU加速,可并行加速的HPC特性,適配于半導體、計算機、通信網絡、車用電子等多個行業的設計和仿真。

本次案例展現了ACEM對于DDR5內存的優化。在云計算、大數據分析、虛擬化等大規模數據中心;人工智能和深度學習領域;科學計算、工程模擬、氣象預測等高性能計算領域,ACEM都能夠在實際應用層面,提供參考與借鑒。

PART2 場景描述

現在電子系統設計中,基于DDR5總線技術的擴展應用越來越多,而DDR5總線的最高傳輸速率已經達8.4GT/s。如何保證DDR5總線傳輸的信號質量,在特定板材下的傳輸距離長度是多少,等等,都已成為電子系統設計必需面對的設計難題。

本案例針對DDR5總線的高速率、高帶寬、高性能以及點對點傳輸方式的特點,展開了基于POP結構的DDR5鏈路設計與信號完整性(SI)仿真技術的研究,并結合上述問題對所設計的鏈路進行SI仿真,詳細分析仿真結果,以此來研究DDR5的數據傳輸速度和吞吐量等信號完整性問題。

PART3 案例簡介

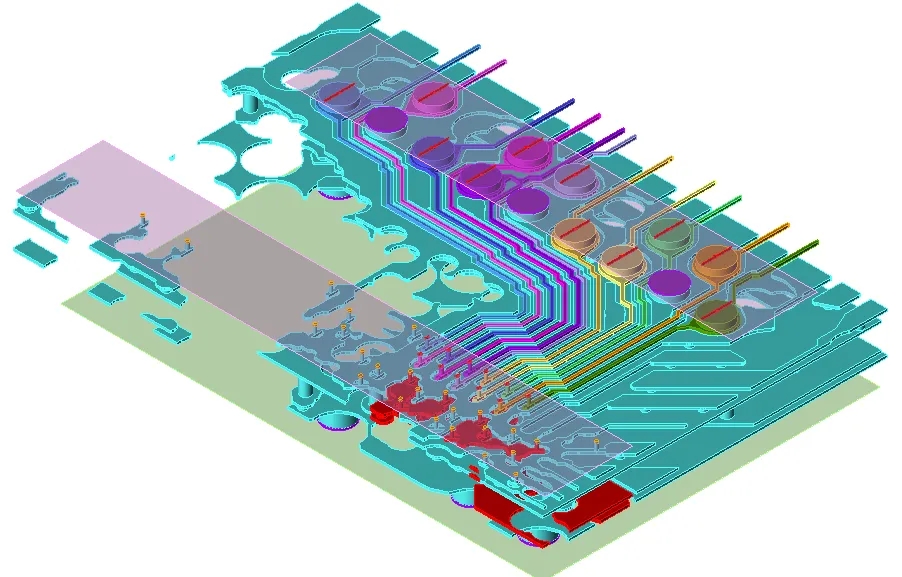

此案例為POP的封裝設計,用戶通過ACEM來優化高速并行接口走線設計,使信道質量符合設計要求。模型如下圖所示:

PART4 仿真設置

4.1 生成仿真模型,選擇Net和Component設置

Net Editor 區域選擇一組DDR信號進行仿真、勾選相關參考電源、參考地網絡;

Component Editor 區域設置焊球、port相關參數;

在 Information 區域選擇仿真模式,點擊 Generator cut model 即可生成模型。

4.2 設置仿真參數

PART5 仿真效果

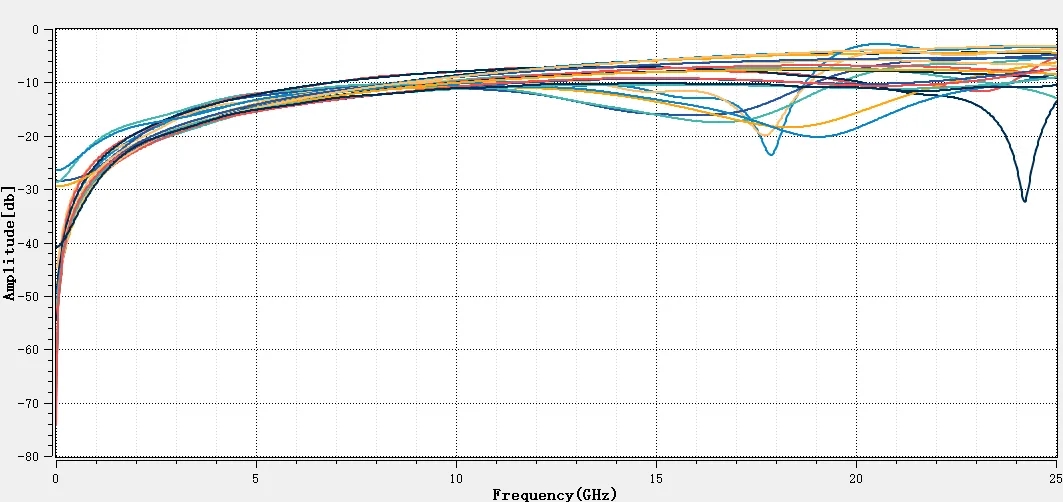

5.1 S參數分析

回損:DQ0-DQ7回損在10G以內滿足-10db的要求。

插損:其他端口滿足在-3db以上,DQ0的信號未滿足要求。

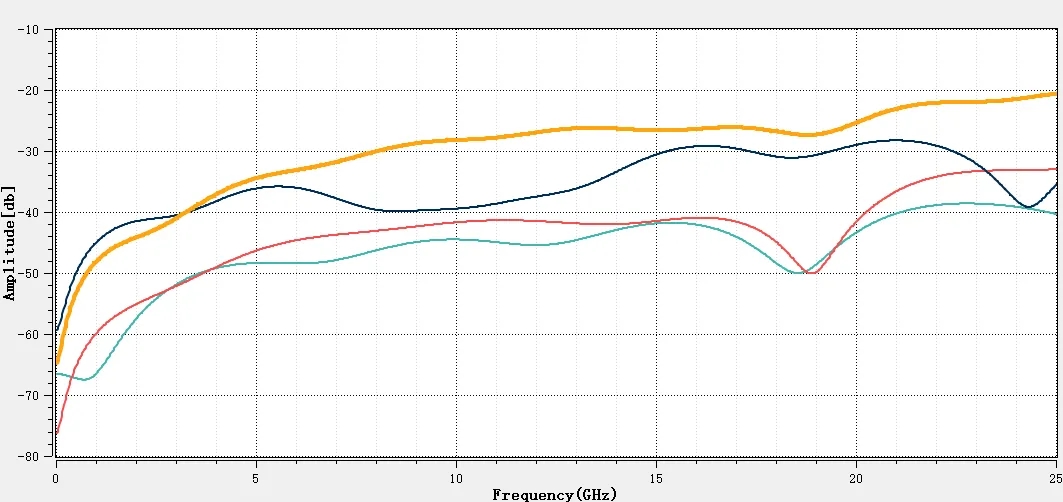

串擾:其他端口滿足在-30db以下,DQ5的信號未滿足要求。

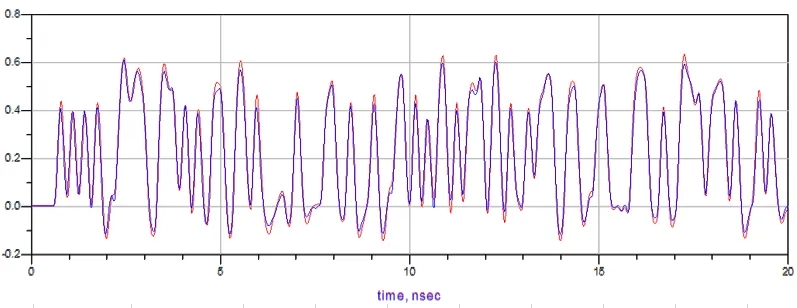

從眼圖可以看出在6400Mbps的眼高為:0.173,眼寬為9.062E-11。

發現眼睛張開不是很理想,通過在接收端設置均衡調整之后,眼寬和眼高在6400Mbps能夠滿足要求,以及通過合適的信號線寬度和阻抗匹配,減少傳輸線的功率衰減和反射。使用終端匹配電阻,降低信號反射和串擾的影響。在電路板設計中增加地平面和電源層,以提供足夠的屏蔽和隔離,合適地布局阻擋層,減少信號之間的干擾,優化后串擾滿足相關技術性指標。

PART6 ACEM在此案中的價值點

在現代計算系統中,DDR5(第五代雙倍數據率)是一種高性能的內存標準,可以提供更高的數據傳輸速度和吞吐量。為了確保DDR5在實際應用中具有穩定和可靠的性能,進行并行仿真以評估其信號完整性是至關重要的。

本案例通過ACEM仿真軟件仿真對DDR5信號的SI分析,得出最高速率信號在頻域的spec,提出改善信號傳輸質量、保證信號完整性的方法, 為實際應用提供了有益參考與借鑒。